�ɵ�Ƭ�����ɵ����ʵ��ƽ̨Ӳ�����

1.����ע���¼,֧��������ʾ�������ɻ�ȡ������.

2.��������ҳ���ܵ�Ϊ,���غ���ˮӡ.����ѧϰ�ο�֮��.

�� �� �� ��������

�ɵ�Ƭ�����ɵ����ʵ��ƽ̨Ӳ�����(��������,���ⱨ��,���ķ���,��ҵ����13500��)

ժҪ���ִ�ͨ��ϵͳ�У�Ϊȷ��ͨ�ŵ��ȶ���ɿ�����ͨ���豸��Ƶ��ȷ�ʺ��ȶ�������˼��ߵ�Ҫ��ͳ��RC��LC�ź�Դ��Ȼ���ڷ��㣬�����ȶ��Բ��ߣ���ʹ��ʯӢ����������Ȼ�ȶ��Թ��ߣ���������Ƶ�ʵ��ڷ�Χ�ֲ����������ִ����Ƶ�ʺϳ���������������ʹƵ�ʵĵ��ڷ�Χ�ﵽҪ���������ȶ��Թ��ߡ������ִ����Ƶ�ʺϳɼ��������ں�δ����ͨ�����������Ҫ�����á�

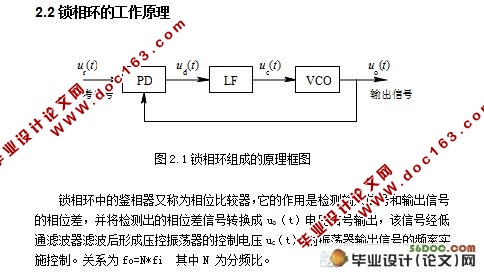

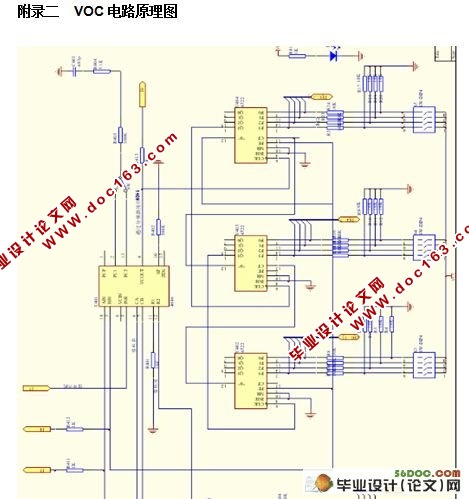

����ɼ���������·�˲�����ѹ��������ɡ���������Ҫ���ڼ�����������ź�ֱ�ӵ���λ֮������������λ�Ƚ�����ѹ������VCO�����LM4046 ��ɡ�1/N��Ƶ��·��һ��������Ԥ������Ƶ�������������ÿ�Ԥ����BCD��ͬ��1/N�Ƽ�����MC14522��ÿ���ķ�Ƶ�ȿ���4 λС�Ͳ���������8421BCD����ʽ�Ըü�����������Ԥ��������Ƶ�ȿ�ѡ��ķ�ΧΪ0——999������·����������ź�Դ ������·������õ�ѹ��������Ƶ�� ����·��������״̬��VCO����Ƶ�� =N ���ı����������Ƶ���ķ�Ƶ��Nʱ��VCO����Ƶ�� Ҳ���ű仯��ͬʱҲ�����õ�Ƭ�����ӿ��Ƶ�·��ͨ�������������������Ʒ�Ƶ�ȡ���������ʵ��Ƶ�ʺϳɵĹ��̡� [��Ȩ���У�http://DOC163.com]

�ؼ��ʣ���� Ƶ�ʺϳ��� ��Ƶ��

The hardware design of the PLL experimental platform based on MCU

Abstract: In order to ensure the stabilization and reliability of the communications, the modern communication systems have offered high requirements on the accuracy and stabilization in the frequency of communication equipment. Though the signal of RC or LC is adjusted conveniently, it is not steady enough. Also, the quartz crystals oscillator has a high stabilization, but the its frequency adjustment range is not enough. Using the technology of modern PLL Frequency Synthesizer, it can bring the frequency adjustment range up to the required standard and its stabilization is high enough. The technology of the modern PLL Frequency Synthesizer, takes an important part in present and future field of communication.

PLL is made up of phase detector, loop filter and voltage control oscillator. Phase detector is used by detecting the direct phase separation of the two input signals. In this design, the phase comparator and the voltage control oscillator VCO comprise PLL LM4046. 1/N scale down circuit is a three-grade frequency divider and each grade uses BCD code synchronous and 1/N counter MC14522. The input frequency of each grade gauges the initialized data base to its counter in the form of 8421BCD code, by using four small toggle switches. The optional scope of the input frequency is 0-999. When inputting the external signal generator , it received the oscillator frequency under the circuit feedback, the circuit is on the locked status, the oscillator frequency of VCO equals to N . With the changing of the input frequency N, the oscillator frequency of VCO is changing too. This is the process of frequency synthetic. [������Դ��http://www.doc163.com]

KeyWords: PLL , frequency Synthesizer, frequency dividing ratio

.

3 ϵͳ���巽�����

�õ�Ƭ��ʵ�ֵ���ʽ����Ƶ�ʺϳ������ɵ����ʵ��ƽ̨�����м����������ʾ���ܣ����Ƶ��f0=1.000~999KHZ, Ƶ�ʼ��1KHZ�������ƽ��TTL��ƽ����Դ��+5v��ͨ��ʵ���豸�ܹ۲������ͬ�����̡����ٹ��̡������̣����������ͬ�����벶�������������ǵĴ������ܲ������������źŵIJ��Σ��������۲���С��Ƶ�Ⱥ�����Ƶ�ȡ�

3��1 ϵͳ����Ӳ����Ʒ���

ʵ��Ƶ�ʺϳɵķ����ж��֣�����ֱ�Ӻϳɣ����ʽ�������ʽ��ʵ�ַ������ж��֣�����ɱ侧��Ҳ�ɱ��Ƶϵ��M���������õ�Ƭ����ʵ�ֵȵȡ�������Dz��õ�Ƭ����ʵ��Ƶ�ʺϳɣ�ϵͳ��ͼ��ͼ3.1��ʾ��

3.1.1 �����·���

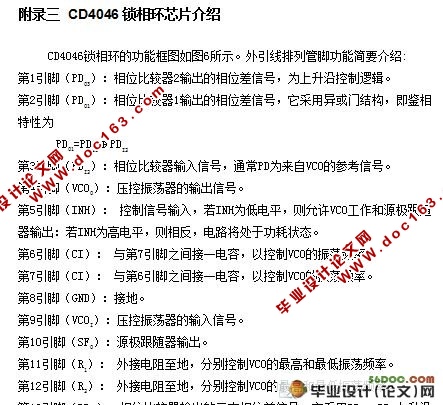

�������оƬCD4046����CMOS��·���ɵĶ�ܵ�Ƭ������������й��ĵ͡������迹�ߡ���Դ��ѹ��Χ�����ŵ㡣���źŴ���������ϵͳ�У�CD4046���õ��˹㷺��Ӧ�ã���������Ƶ�ʵ��ơ�Ƶ��������ʱ��ͬ����Ƶ�ʺϳɵȷ���

Ŀ¼ [������Դ��http://www.doc163.com]

1 ���� 1

1.1 ѡ����������� 1

1.2 ����ķ�չ 1

2 �����Ƶ�ʺϳ��� 3

2.1������ص� 3

2.2����Ĺ���ԭ�� 4

2.3 �����Ӧ�� 8

2.4 Ƶ�ʺϳ������ 8

2.4.1 Ƶ�ʺϳ������似��ָ�� 8

2.5 Ƶ�ʺϳ��������ͪ� 9

2.5.1 ֱ��ʽƵ�ʺϳ�����DS�� 9

2.5.2 ���ʽƵ�ʺϳ�����IS�� 9

2.5.3 ֱ������ʽƵ�ʺϳ�����DDS�� 10

3 ϵͳ���巽����� 11

3��1 ϵͳ����Ӳ����Ʒ��� 11

3.1.1 �����·��� 12

3.1.2��Ƶ��·��� 15

3.1.3 ��Ƭ����Сϵͳ��·��� 18

3.1.4 ������ʾģ����� 20

3.2������� 23

4. ʵ����� 24 [������Դ��http://Doc163.com]

4.1 ����ʽ����Ƶ�ʺϳ�������ԭ�� 24

4.2�������ʵ�� 27

4.3 ���Ƶ�ʺϳ������� 28

�ܽ� 30

����� 31

��л 32

��¼ 33

[������Դ��http://doc163.com]

��һƪ���ɵ�Ƭ�����ɵ����ʵ��ƽ̨�������

��һƪ��������������ģ���ң��С����·���